Archive

ST/Freescale intro 32-bit MCUs for safety critical applications

Early this month, STMicroelectronics and Freescale Semiconductor introduced a new dual-core microcontroller (MCU) family aimed at functional safety applications for car electronics.

These 32-bit devices help engineers address the challenge of applying sophisticated safety concepts to comply with current and future safety standards. The dual-core MCU family also includes features that help engineers focus on application design and simplify the challenges of safety concept development and certification.

Based on the industry-leading 32-bit Power Architecture technology, the dual-core MCU family, part-numbered SPC56EL at ST and MPC564xL at Freescale, is ideal for a wide range of automotive safety applications including electric power steering for improved vehicle efficiency, active suspension for improved dynamics and ride performance, anti-lock braking systems and radar for adaptive cruise control.

Freescale/STMicroelectronics JDP

The Freescale/STMicroelectronics joint development program (JDP) is headquartered in Munich, Germany, and jointly managed by ST and Freescale.

The JDP is accelerating innovation and development of products for the automotive market. The JDP is developing 32-bit Power Architecture MCUs manufactured on 90nm technology for an array of automotive applications: a) powertrain, b) body, c) chassis and safety, and d) instrument cluster.

STMicroelectronics’ SK Yue, said: “We are developing 32-bit MCUs based on 90nm Power Architecture technology. One unique feature — it allows customer to use dual core or single core operation. The objective of this MCU is to help customers simplify design and to also reduce the overall system cost.

On the JDP, he added: “We will have more products coming out over a period of time. This JDP is targeted toward automotive products.”

Commenting on the automotive market today, he said that from June onward, the industry has been witnessing a gradual sign of recovery coming in the automotive market.

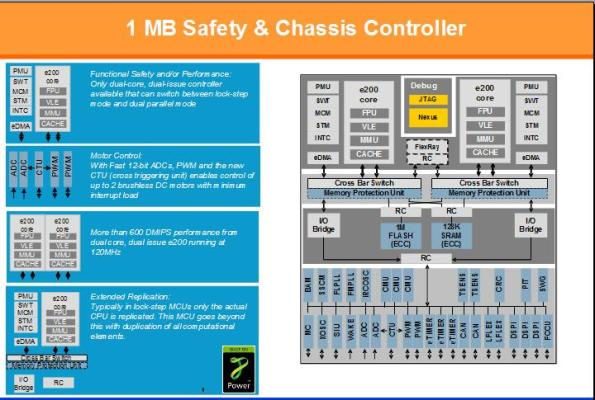

1 MB safety and chassis controller -- 32-bit MCU courtesy Freescale/STMicroelectronics joint development program (JDP)

Automotive market challenges

There has been an increasing integration and system complexity. These include:

* Increasing electrification of the vehicle (replacing traditional mechanical systems).

* Mounting costs pressure leading to integration of more functionality in a single ECU.

* Subsequent increase in use of high-performance sensor systems has driven increased MCU performance needs.

There are also increasing safety expectations. Automotive system manufacturers need to guarantee the IEC61508 (SIL3) and ISO26262 (ASILD) system-safety capability. Also, a move from passive to active safety is increasing the number of safety functions distributed in many ECUs.

Finally, there is a continued demand for quality — in form of zero defects, by which, a 10x quality improvement is expected.

MCU family addresses market challenges

The MCU family offers exceptional integration and performance. These include: high-end 32-bit dual-issue Power Architecture cores, combined with comprehensive peripheral set in 90nm non-volatile-memory technology. It also provides a cost effective solution by reducing board size, chip count and logistics/support costs.

It also solves functional safety. The Functional Safety architecture has been specifically designed to support IEC61508 (SIL3) and ISO26262 (ASILD) safety standards. The architecture provides redundancy checking of all computational elements to help endure the operation of safety related tasks. The unique, dual mode of operation allows customers to choose how best to address their safety requirements without compromising on performance.

The MCU also offers best-in-class quality. It is design for quality, aiming for zero defects. The test and manufacture have been aligned to lifetime warranty needs.

The MCU family addresses the challenges of applying sophisticated safety concepts to meet future safety standards. Yue added, “There are two safety standards — we are following those guidelines.” These are the IEC61508 (SIL3) and ISO26262 (ASILD) system-safety capabilities.

The automotive industry is also targeting for zero defects. “Therefore, all suppliers in tier 1 and 2 need to come up with stringent manuyfaturing and testing process that ensures zero defects,” he said.

32-bit dual-issue, dual-core MCU family

Finally, why dual core? Yue said that the MCU helps customers to achieve to achieve safety and motor control. Hence, dual core will definitely help deliver results.

“In many automotive applications, especially in safety-related applications, we want to have redundancy for safety. In the lock-step mode, two cores run the same task simultaneously, and results are then compared to each other in every computation. If the results are not matched, it indicates that there are some problems.”

This MCU family definitely simplifies design. It uses a flexible, configurable architecture that addresses both lock-step and dual parallel operation modes on a single dual-core chip. Next, it complies with safety standards.

A redundant architecture provides a compelling solution for real-time applications that require compliance with the IEC61508 SIL3 and ISO26262 ASIL-D safety standards. It also lowers the systems cost.

Dual-core architecture reduces the need for component duplication at the system level, and lowers overall system costs.

Growth drivers for semiconductor industry

Michael J. Fister, president and CEO, Cadence Design Systems Inc., who was in India for the CDNLive event, delivered a wonderful keynote at the recently held CDNLive. Here’s what he had to say!

The semiconductor industry is maturing. Since 2000, the industry’s annual growth rate has experienced extreme highs and lows.

Though the semiconductor industry’s revenue growth will be low in 2007, the good news is that growth rates are smoothing out as costly fabs demand consistent production. Wireless communications, computers, and consumer products continue to be the growth drivers for semiconductors. A couple of the semiconductor technology trends driving electronic design and product development are:

* More designs at advanced nodes — Beginning this year, 90nm designs will outnumber those at 130nm. Meanwhile, 65nm is design activity is ramping up and advanced designs are targeting 45nm.

* Growth in transistor count and logic — Not only are transistor counts increasing according to Moore’s Law, those transistors are being used to create more functions -– and therefore more complexity -– on a single chip, not just adding memory to the existing designs.

A related trend is that the amount of chip production outsourced to foundries continues to grow, with many Integrated Device Manufacturers (IDMs) moving to a ‘Fab-lite’ strategy for advanced nodes. This is happening as design is becoming a greater product differentiation than production.

Note that Fister’s reference to Fab-lite is interesting, even though lot of new investments are said to be getting into, and he himself says, “costly fabs demand consistent production.” There is another point that should not be overlooked — the one concerning Qualcomm, a fabless company, making it to the Top 10 semicon companies, for the first time.

Coming back the Cadence CEO, all of these trends create two kinds of challenges for chip design. These are: 1) manufacturability at advanced process nodes like 90nm and below, and 2) increased complexity and scale of chip design of system-on-chip (SoC).

Design solutions today must address these challenges, and increase team productivity and schedule predictability. To accomplish this, Cadence is focused on a holistic approach to the design flow. The Cadence Low-Power Solution and the Encounter Timing System are good examples of this holistic approach addressing the challenges of escalating scale and complexity.

The same holistic approach is shown in Cadence’s approach to manufacturability, which is to integrate design for manufacturability (DFM) into all aspects of the design flow, rather than just apply DFM techniques as a post-design step.